Caches!

Overview

As part of my Computer Architecture module , built a Cache simulator in C++.

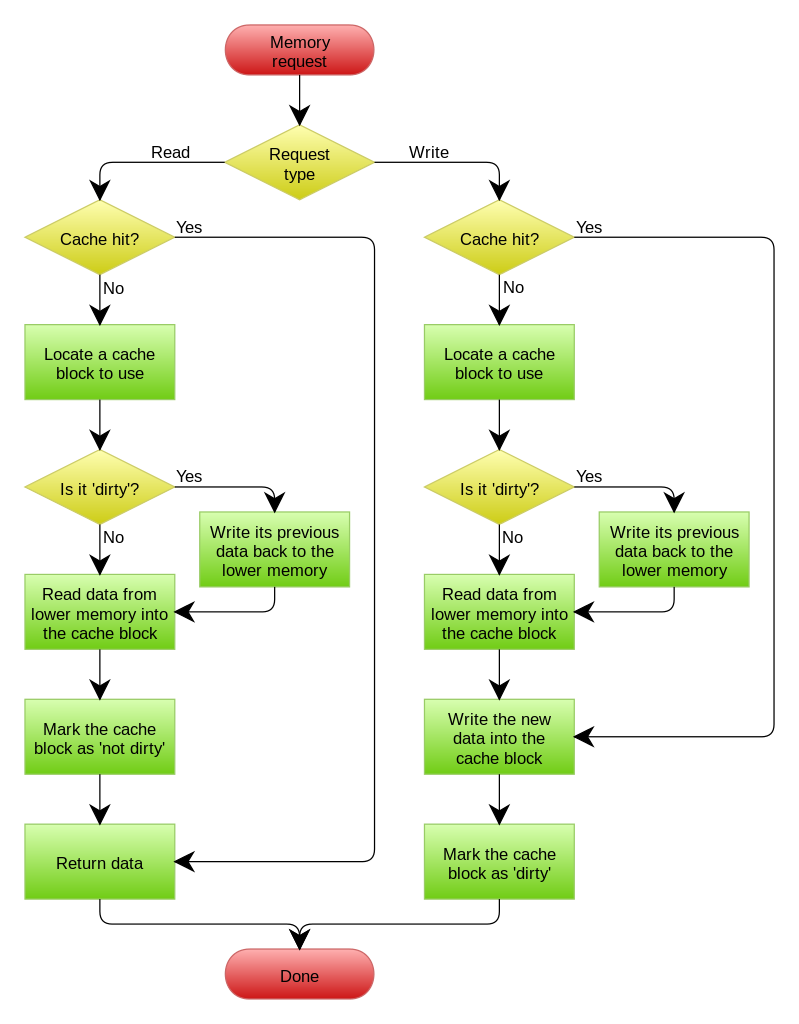

A key part of building the cache simulator was understanding how the different types of caches - Direct Mapped, Set associative , Fully associative work and also understanding cache write-back policy and the Least Recently Used(LRU) policy as the Replacement policy.

Also fundamental was the understanding the handling of valid bits and dirty bits in a Cache with a write-back policy.

Goal

The end goal of the project was to simulate a Level 1 cache by accepting memory access requests and debug requests from standard input and maintain concsistency between cache and the main memory.

Also , some optimizations like write miss optimizations for a single block direct mapped cache were implemented.

Procedure

The diagram above is the central logic required for handling dirty bits in Caches. Kindly see the github page for all the details of the specification, procedure and the conclusion.

.jpg)